随着集成电路进入超大规模集成电路时代,电路设计的复杂性大大增加,完成一个电路测试所需的时间和投入也越来越大, 同时产品的设计周期却越来越短。为了节省设计和测试的时间,加快产品上市进程,除了采用先进的测试方法外, 提高设计本身的可测试性也将是一个行之有效的方法。Mentor Graphics公司副总裁及Design-to-Silicon部门总经理Joseph Sawicki表示:“可测试性设计(Design for Testability,DFT)在不断推进的先进工艺节点和越来越复杂的设计中将成为至关重要的一环,设计公司对于完整、可测试性方法的需求也将不断增加。”

他表示:“Mentor Graphics对于DFT测试非常重视,目前已占据了该市场超过一半的市场份额,主要关注三个重要的测试领域:测试品质、测试复杂性和成本、测试失败诊断和良率分析。”

许多行业尤其是汽车行业对于安全的需求特别严格,零缺陷(DPM)不只是一个目标,而是必须要达成的要求,另外,新标准(如ISO 26262)对于安全和质量等方面也都提出了更严格的要求,这些原因导致了测试品质也必须越来越高。此外,3D IC技术以及新工艺技术(如FinFET和FDSOI)的应用,可以预见出现缺陷的概率将增加,传统的门级抽象和固定故障模型已经无法保证高品质和低缺陷率的测试需求。MentorGraphics提供的Cell-aware ATPGTest支持晶体管级的测试,是基于实际的单元布局检测内部存在的但原本无法检测的缺陷的测试工具,可以帮助用户大大提高测试品质。

Joseph Sawicki表示:“标准的门级‘固定型’故障模型将可能无法在越来越复杂的标准单

元中检测出全部的内部缺陷,而Cell -aware ATPG Test提供的故障模型是晶体管级,能帮助用户尽可能地发现内部存在的缺陷,尤其是在未来先进工艺和技术普及应用后,这样的测试需求将更加突出。

针对测试复杂性和成本,Mentor Graphics所提供的工具Tessent Test Kompress可以帮助用户自动生成压缩10 0倍及以上的测试向量,减少测试时间和测试数据量,大大节省ATPG 的运行时间和内存的使用,同时实现低DPM以及最好的测试品质。把Test Kompress和LBIST(内建自测逻辑)整合使用,可以进一步扩大缺陷检测的区域,缩短测试的时间,同时满足生产和系统内测试的需求。Joseph Sawicki强调:“这两个功能模块的组合可以满足那些需要上电自检(Power-on self-test)的应用。”

Tessent Diagnosis和Tessent YieldInsight则是Mentor Graphics针对测试失败诊断和良率分析开发的工具。Tessent Diagnosis可以将错误的测试周期数据转换为有价值的良率分析数据,可大大减少寻找良率损失根本原因的时间。传统的诊断只能对逻辑网络进行解析,而Tessent Diagnosis的Layout-aware可以进行物理段的分析,精确缺陷存在的位置和原因,大大提高诊断在良率分析中的价值。Tessent YieldI nsight则是一种通过分析测试数据进行良率损失分析的软件,Joseph Sawicki列举了一个Tessent YieldInsight实际使用的例子,在飞思卡尔9 0 nm SoC的生产中,利用Tessent YieldInsight发现了4个系统级的问题,目前成熟良率已达95%。

针对D F R ( Design for Re -liability),此次Joseph Sawicki也宣布了其Calibre PERC验证产品成为了TSMC用于IP质量项目(TSMC9000)的验证工具,可以帮助TSMC或其IP合作伙伴对开发的IP或第三方提供的IP进行预验证,保证IP的可靠性、高品质以及鲁棒性(Robustness)。

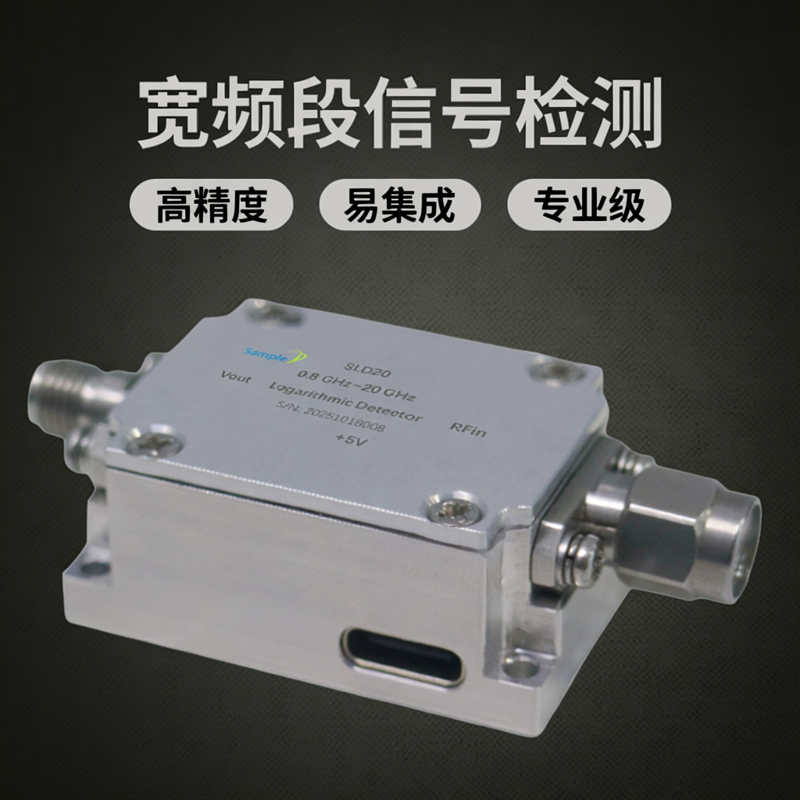

线性vs对数检波器:盛铂科技SMA与SLD系列选型指南

2026-03-12

点击查看详细>>

线性vs对数检波器:盛铂科技SMA与SLD系列选型指南

2026-03-12

点击查看详细>>

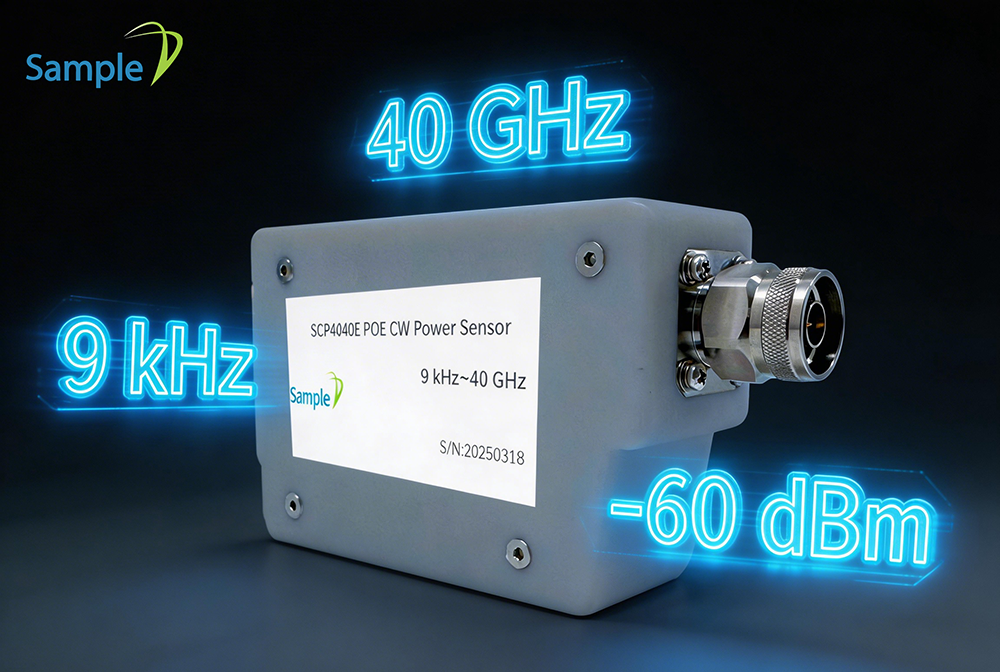

2026年USB射频微波功率计选购避坑指南:这5个功能必须有

2026-03-10

点击查看详细>>

2026年USB射频微波功率计选购避坑指南:这5个功能必须有

2026-03-10

点击查看详细>>

功率测量:连续波信号 vs. 脉冲信号

2026-03-04

点击查看详细>>

功率测量:连续波信号 vs. 脉冲信号

2026-03-04

点击查看详细>>

可编程噪声发生器(噪声信号源)设备如何选型?收下这份避坑指南

2026-03-02

点击查看详细>>

可编程噪声发生器(噪声信号源)设备如何选型?收下这份避坑指南

2026-03-02

点击查看详细>>

功率计/功率传感器怎么选?避坑指南

2026-02-28

点击查看详细>>

功率计/功率传感器怎么选?避坑指南

2026-02-28

点击查看详细>>

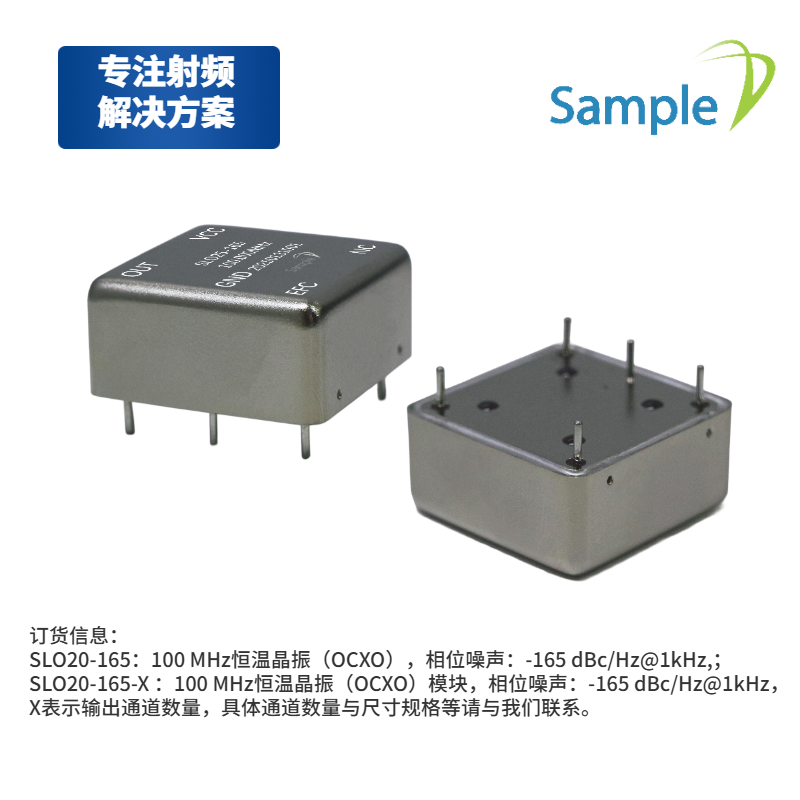

高稳定度晶振怎么选?OCXO、TCXO、普通晶振区别

2026-02-12

高稳定度晶振怎么选?OCXO、TCXO、普通晶振区别

2026-02-12

晶振是所有电子系统的时钟基准,在射频微波设备中,晶振直接决定频率源、信号源、测试仪器的精度与稳定度。本文讲透晶振选型。

点击查看详细>>